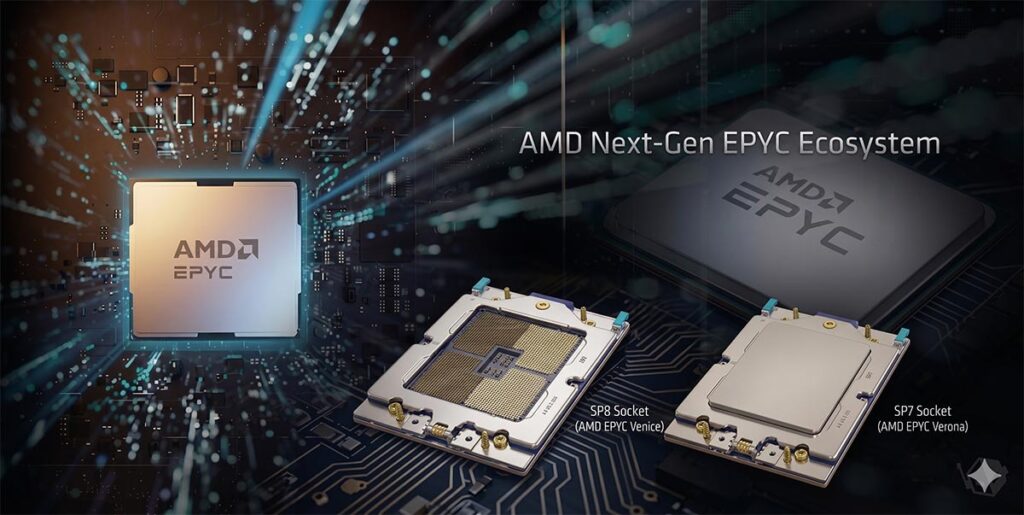

AMD รุกหนักตลาดเซิร์ฟเวอร์ เปิดรายละเอียดซ็อกเก็ตใหม่ SP7 และ SP8 รองรับขุมพลัง EPYC Venice สถาปัตยกรรม Zen 6 📍

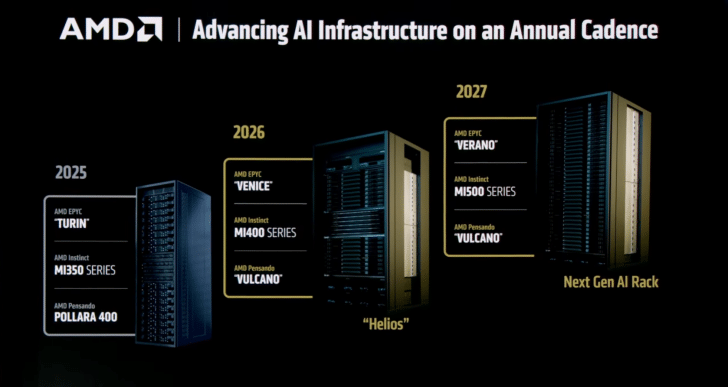

AMD EPYC Venice เตรียมสร้างมาตรฐานใหม่ให้กับอุตสาหกรรมศูนย์ข้อมูล (Data Center) ด้วยการเปิดตัวรายละเอียดของซ็อกเก็ตเจเนอเรชันถัดไปอย่าง SP7 และ SP8 ซึ่งถูกออกแบบมาเพื่อรองรับหน่วยประมวลผลตระกูล EPYC Venice และ Verano บนสถาปัตยกรรม Zen 6 โดยเน้นการเพิ่มความหนาแน่นของการคำนวณ (Compute Density) และประสิทธิภาพการเชื่อมต่อที่รวดเร็วกว่าเดิม 💻

เจาะลึกรายละเอียดซ็อกเก็ต SP7 และ SP8: ใหญ่ขึ้นและทรงพลังกว่าเดิม

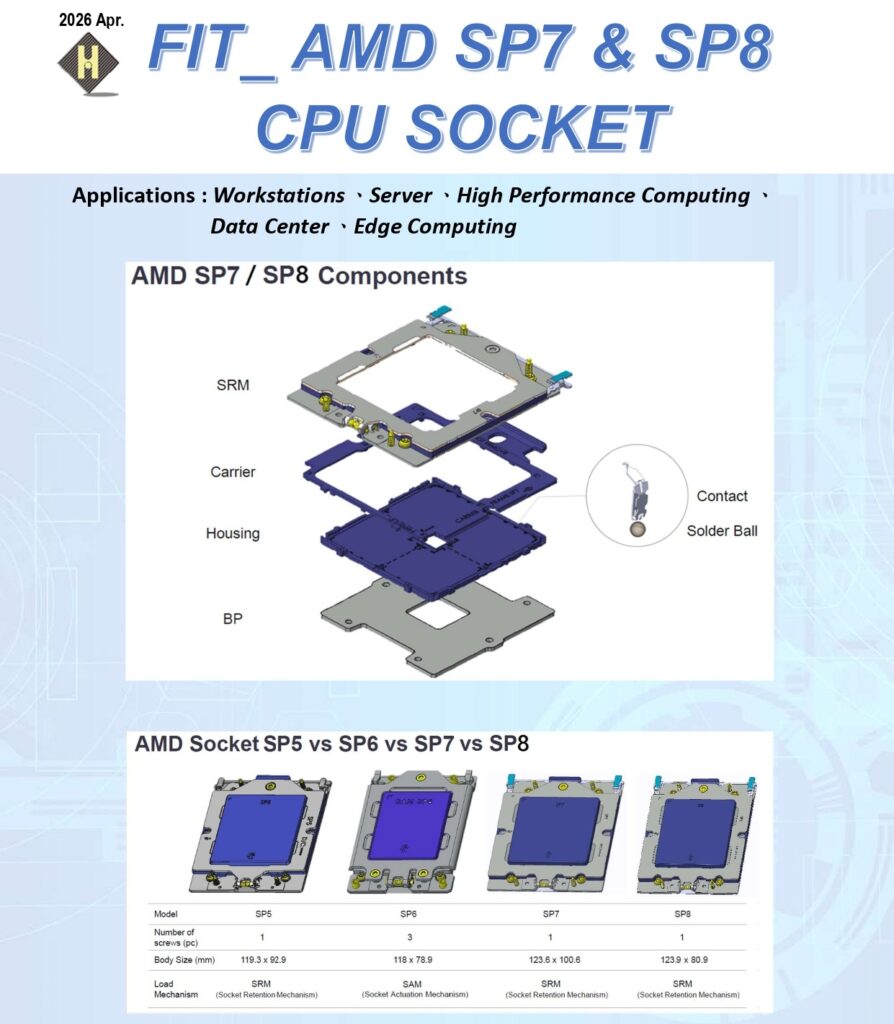

จากการเปิดเผยข้อมูลโดย HELM Technology ผู้ผลิตส่วนประกอบอิเล็กทรอนิกส์ชั้นนำจากไต้หวัน พบว่าซ็อกเก็ตใหม่ทั้งสองรุ่นมีขนาดที่ใหญ่ขึ้นกว่ารุ่นปัจจุบันอย่างมีนัยสำคัญ เพื่อรองรับจำนวนคอร์และช่องสัญญาณที่เพิ่มมากขึ้น

-

ซ็อกเก็ต SP7: ออกแบบมาสำหรับ EPYC Venice โดยมีขนาดตัวถัง 123.6 x 100.6 มม. ซึ่งใหญ่กว่าซ็อกเก็ต SP5 (ที่ใช้ในรุ่น Genoa และ Turin) ถึง 12% โดยยังคงใช้กลไกการยึดแบบ SRM (Socket Retention Mechanism) เพื่อความมั่นคงในการติดตั้ง

-

ซ็อกเก็ต SP8: มุ่งเน้นไปที่กลุ่มคุ้มค่า (Cost-effective) สำหรับชิปตระกูล Verano มีขนาด 123.9 x 80.9 มม. ซึ่งใหญ่กว่าซ็อกเก็ต SP6 เดิมประมาณ 7% และมีการเปลี่ยนมาใช้กลไก SRM แทนระบบ SAM เดิมเพื่อให้รองรับการทำงานในระดับสูงได้ดีขึ้น

ประสิทธิภาพแพลตฟอร์ม SP7 และ SP8 ที่ก้าวกระโดด 🚀

แพลตฟอร์มใหม่นี้ถูกออกแบบมาเพื่อรองรับภาระงานหนักในระดับ Enterprise โดยเฉพาะ โดยมีความแตกต่างทางเทคนิคที่น่าสนใจดังนี้:

แพลตฟอร์ม SP7 (ระดับ High-end)

-

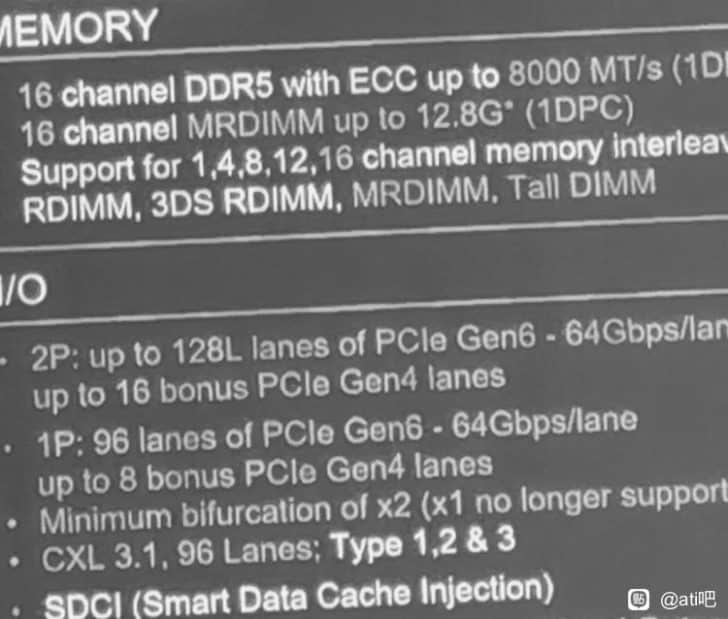

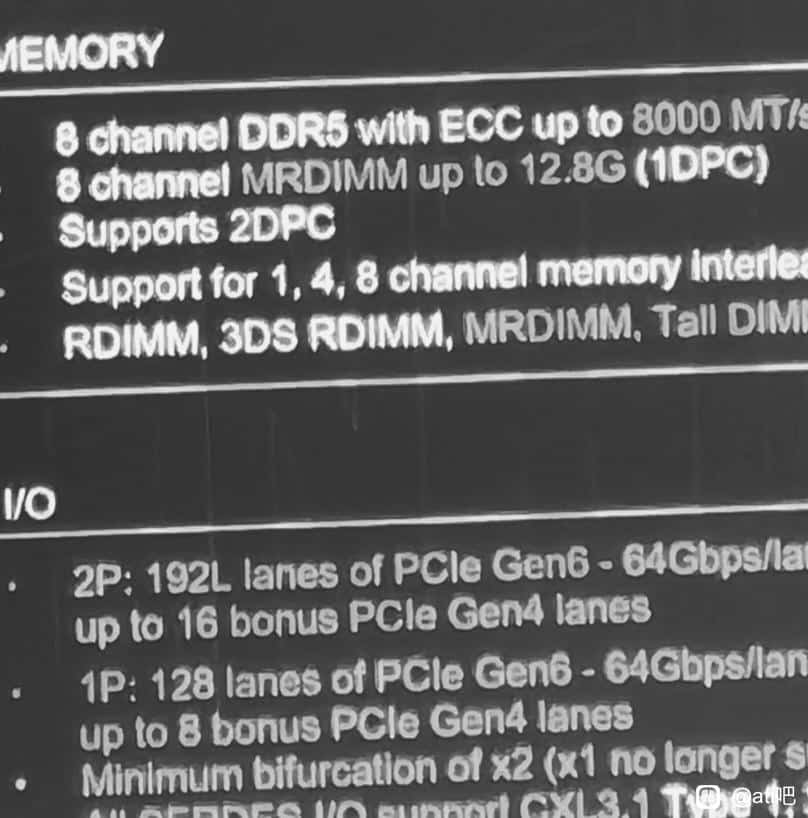

หน่วยความจำ: รองรับ DDR5 สูงสุดถึง 16 แชนเนล ความเร็วสูงสุด 8,000 MT/s และรองรับ MRDIMM สูงสุดถึง 12,800 MT/s 🧠

-

I/O และการเชื่อมต่อ: รองรับ PCIe Gen 6.0 สูงสุด 128 เลน (สำหรับระบบ 2P) ให้แบนด์วิดท์มหาศาลถึง 64 Gbps ต่อเลน

แพลตฟอร์ม SP8 (ระดับ Entry-level)

-

หน่วยความจำ: รองรับ DDR5 แบบ 8 แชนเนล แต่ยังคงรักษาความสามารถในการรองรับความเร็วเทียบเท่ากับ SP7

-

ความพิเศษของ I/O: แม้จะเป็นรุ่นรอง แต่ SP8 กลับรองรับ PCIe Gen 6.0 ได้สูงสุดถึง 192 เลนในระบบ 2P ซึ่งออกแบบมาเพื่อเพิ่มขีดความสามารถในการขยายระบบจัดเก็บข้อมูลและเครือข่าย

ข้อมูลทางเทคนิคของชิป Zen 6: จำนวนคอร์ที่มากขึ้น

ชิป AMD EPYC Venice รุ่นใหม่ที่ใช้สถาปัตยกรรม Zen 6C จะมาพร้อมกับจำนวนคอร์สูงสุดถึง 256 คอร์ (512 เธรด) โดยแบ่งเป็น 8 CCD ซึ่งแต่ละ CCD บรรจุคอร์ได้ถึง 32 คอร์ พร้อมหน่วยความจำแคช L3 รวมทั้งชิปสูงถึง 1 GB ⚙️

ในขณะที่รุ่นมาตรฐานของ Venice และ Verano จะมี 12 คอร์ต่อ CCD รวมสูงสุด 96 คอร์ แต่จะได้รับการอัปเกรดแคช L3 เพิ่มขึ้น 50% เมื่อเทียบกับสถาปัตยกรรม Zen 5 เดิม ซึ่งจะส่งผลโดยตรงต่อความเร็วในการประมวลผลข้อมูลที่ซับซ้อน

FAQs | คำถามที่พบบ่อย 💬

1. AMD EPYC Venice และ Verano จะวางจำหน่ายเมื่อใด?

-

ตามแผนงาน (Roadmap) ปัจจุบัน EPYC Venice มีกำหนดการเปิดตัวในปี 2026 และจะตามมาด้วยตระกูล Verano ในปี 2027

2. ซ็อกเก็ต SP7 และ SP8 สามารถใช้ร่วมกับเมนบอร์ดรุ่นเก่าได้หรือไม่?

-

ไม่ได้ เนื่องจากซ็อกเก็ตใหม่มีขนาดกายภาพที่ใหญ่ขึ้นและมีการเปลี่ยนโครงสร้างหน้าสัมผัสเพื่อรองรับ PCIe 6.0 และ DDR5 แบบหลายแชนเนล ผู้ใช้จำเป็นต้องใช้เมนบอร์ดรุ่นใหม่ที่รองรับ

3. การใช้พลังงาน (TDP) ของชิปรุ่นใหม่เป็นอย่างไร?

-

ชิปบนแพลตฟอร์ม SP7 คาดว่าจะมีค่า TDP สูงถึง 600W เนื่องจากประสิทธิภาพที่เพิ่มขึ้น ส่วนแพลตฟอร์ม SP8 จะอยู่ที่ประมาณ 350-400W

สรุปข่าว 🇹🇭

การเปิดตัวรายละเอียดซ็อกเก็ต SP7 และ SP8 สำหรับ AMD EPYC Venice สะท้อนให้เห็นถึงความมุ่งมั่นของ AMD ในการครองตลาด Data Center ด้วยเทคโนโลยีที่ล้ำสมัย ทั้งการรองรับ PCIe Gen 6.0 และจำนวนคอร์มหาศาลถึง 256 คอร์ ซึ่งการขยายขนาดของซ็อกเก็ตและการเพิ่มช่องสัญญาณหน่วยความจำจะช่วยตอบโจทย์ความต้องการด้าน AI และการประมวลผลระบบคลาวด์ในอนาคตได้อย่างมีประสิทธิภาพ

เครดิต: wccftech.com